ARM ARM Accredited Engineer EN0-001 Exam Dumps: Updated Questions & Answers (April 2026)

During an investigation into a software performance problem an engineer doubles the clock frequency of a cached ARM processor running the software. Unfortunately the performance of the application does not increase by very much, despite running on the processor for 100% of the time. What is likely to be the main bottleneck in the system?

Optimizing for space will:

Which of the following would enable the use of a symmetric multiprocessing (SMP) operating system?

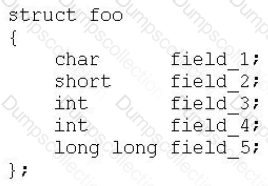

According to the EABI. what would the C size of () operator return when given the following structure?

Which of the following is preserved in dormant mode?

A standard performance benchmark is being run on a single core ARM v7-A processor. The performance results reported are significantly lower than expected. Which of the following options is a possible explanation?

In a Cortex-A processor, after which TWO of these events is a cache maintenance operation required to ensure reliable code execution? (Choose two)

When timing a critical function for an algorithm, using platform time functions such as get time of day (), the result is unpredictable; there is significant variance in the measured time between different runs of the benchmark. Which of the following strategies would improve the accuracy of the measurement?

To return from a Data Abort handler and re-execute the aborting instruction, what value should be loaded to the PC?

Which privileged mode can kernel code use to get direct access to the User mode registers R13 and R14?